Technologia MOS 6502 - MOS Technology 6502

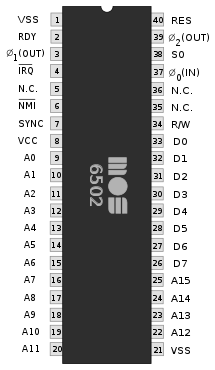

Procesor MOS Technology 6502 w plastikowym opakowaniu DIP-40 . Czterocyfrowy kod daty wskazuje, że powstał w 45 tygodniu (listopad) 1985 roku.

| |

| Informacje ogólne | |

|---|---|

| Wystrzelony | 1975 |

| Wspólni producenci | |

| Wydajność | |

| Maks. Częstotliwość taktowania procesora | 1 MHz do 3 MHz |

| Szerokość danych | 8 |

| Szerokość adresu | 16 |

| Architektura i klasyfikacja | |

| Zestaw instrukcji | MOS 6502 |

| Instrukcje | 56 |

| Specyfikacje fizyczne | |

| Tranzystory | |

| Pakiet(y) | |

| Historia | |

| Poprzednik | |

| Następca | |

MOS Technologia 6502 (zwykle widoczny „sześćdziesięciu pięciu OH dwa” lub „sześciu, pięć, OH dwa”) jest 8-bitowy mikroprocesor , który został opracowany przez mały zespół pod Chuck pedałów na MOS technologii . Zespół projektowy pracował wcześniej w Motoroli nad projektem Motorola 6800 ; 6502 jest zasadniczo uproszczoną, tańszą i szybszą wersją tego projektu.

Kiedy został wprowadzony w 1975 roku, 6502 był ze znaczną marżą najtańszym mikroprocesorem na rynku. Początkowo sprzedawany był za mniej niż jedną szóstą ceny konkurencyjnych projektów większych firm, takich jak 6800 czy Intel 8080 . Jego wprowadzenie spowodowało gwałtowne spadki cen na całym rynku procesorów. Wraz z Zilog Z80 zapoczątkował serię projektów, które doprowadziły do rewolucji komputerów domowych na początku lat 80-tych.

Popularne konsole do gier wideo i komputery, takie jak Atari 2600 , rodzina Atari 8-bit , Apple II , Nintendo Entertainment System , Commodore 64 , Atari Lynx , BBC Micro i inne, korzystają z 6502 lub odmian podstawowej konstrukcji. Wkrótce po wprowadzeniu 6502, technologia MOS została kupiona przez Commodore International , która nadal sprzedawała mikroprocesor i licencje innym producentom. Na początku 6502 był on pozyskiwany przez Rockwell i Synertek , a później licencjonowany przez inne firmy.

W formie CMOS ( 65C02 , który został opracowany przez Western Design Center ), rodzina 6502 jest nadal szeroko stosowana w systemach wbudowanych , a jej wielkość produkcji szacuje się na setki milionów.

Historia i użytkowanie

Początki w Motoroli

6502 został zaprojektowany przez wielu tych samych inżynierów, którzy zaprojektowali rodzinę mikroprocesorów Motorola 6800 . Motorola rozpoczęła projekt mikroprocesora 6800 w 1971 roku z Tomem Bennettem jako głównym architektem. Układ chipów rozpoczął się pod koniec 1972 roku, pierwsze chipy 6800 zostały wyprodukowane w lutym 1974, a cała rodzina została oficjalnie wydana w listopadzie 1974. John Buchanan był projektantem chipa 6800, a Rod Orgill, który później zrobił 6501, pomagał Buchananowi przy analizy obwodów i układ chipów. Bill Mensch dołączył do Motoroli w czerwcu 1971 roku po ukończeniu University of Arizona (w wieku 26 lat). Jego pierwszym zadaniem była pomoc w zdefiniowaniu peryferyjnych układów scalonych dla rodziny 6800, a później był głównym projektantem 6820 Peripheral Interface Adapter (PIA). Inżynierowie Motoroli mogli przeprowadzać symulacje analogowe i cyfrowe na komputerze typu mainframe IBM 370-165 . Bennett zatrudnił Chucka Peddle'a w 1973 roku, aby wykonał prace wspierające architekturę nad produktami rodziny 6800, które są już w toku. Brał udział w wielu dziedzinach, w tym przy projektowaniu 6850 ACIA (interfejs szeregowy).

Docelowymi klientami Motoroli były znane firmy elektroniczne, takie jak Hewlett-Packard , Tektronix , TRW i Chrysler . W maju 1972 roku inżynierowie Motoroli zaczęli odwiedzać wybranych klientów i dzielić się szczegółami proponowanego 8-bitowego systemu mikroprocesorowego z pamięcią ROM, pamięcią RAM oraz interfejsami równoległymi i szeregowymi. Na początku 1974 roku dostarczyli próbki inżynieryjne chipów, aby klienci mogli tworzyć prototypy swoich projektów. Strategia „całkowitej rodziny produktów” Motoroli nie skupiała się na cenie mikroprocesora, ale na obniżeniu całkowitego kosztu projektowania klienta. Oferowali oprogramowanie programistyczne na komputerze z prawem do użytkowania w oznaczonym czasie, system debugowania „EXORciser”, szkolenie na miejscu i wsparcie inżyniera aplikacji w terenie. Zarówno Intel, jak i Motorola początkowo ogłosiły cenę 360 USD za pojedynczy mikroprocesor. Rzeczywista cena za ilości produkcji była znacznie niższa. Motorola zaoferowała zestaw projektowy zawierający 6800 z sześcioma układami pomocniczymi za 300 USD.

Peddle, który towarzyszył sprzedawcom podczas wizyt u klientów, stwierdził, że klienci zniechęcają się wysokimi kosztami mikroprocesorów. Jednocześnie te wizyty niezmiennie powodowały, że inżynierowie, których przedstawiał, tworzyli listy wymaganych instrukcji, które były znacznie mniejsze niż „wszystkie te wymyślne instrukcje”, które były zawarte w 6800. Peddle i inni członkowie zespołu zaczęli nakreślać projekt ulepszona funkcja, zmniejszony mikroprocesor. W tym czasie nowy zakład produkcji półprzewodników Motoroli w Austin w Teksasie miał trudności z produkcją układów MOS, a połowa 1974 roku była początkiem rocznej recesji w branży półprzewodników. Ponadto wielu pracowników Mesa w Arizonie było niezadowolonych z nadchodzącej przeprowadzki do Austin w Teksasie .

Kierownictwo działu produktów półprzewodnikowych Motoroli było przytłoczone problemami i nie wykazywało zainteresowania propozycją tanich mikroprocesorów firmy Peddle. W końcu Peddle otrzymał oficjalny list nakazujący mu zaprzestanie pracy nad systemem. Peddle odpowiedział na polecenie, informując Motorolę, że list stanowił oficjalną deklarację „porzucenia projektu” i jako taka, własność intelektualna, którą opracował do tego momentu, należy teraz do niego. W wywiadzie udzielonym w listopadzie 1975 r. prezes Motoroli, Robert Galvin, ostatecznie zgodził się, że koncepcja Peddle'a była dobra i że dział nie wykorzystał okazji: „Nie wybraliśmy właściwych liderów w dziale produktów półprzewodnikowych”. Dywizja została zreorganizowana, a kierownictwo zastąpione. Nowy wiceprezes grupy, John Welty, powiedział: „Organizacja sprzedaży półprzewodników straciła wrażliwość na potrzeby klientów i nie mogła podejmować szybkich decyzji”.

Przejście na technologię MOS

Peddle zaczął szukać poza Motorolą źródła finansowania tego nowego projektu. Początkowo zwrócił się do dyrektora generalnego Mostek LJ Sevina , ale odmówił. Sevin przyznał później, że obawiał się, że Motorola pozwie ich.

Kiedy Peddle odwiedzał Ford Motor Company podczas jednej ze swoich podróży handlowych, Bob Johnson, późniejszy szef działu automatyzacji silników Forda, wspomniał, że ich były kolega John Paivinen przeniósł się do General Instrument i nauczył się projektowania półprzewodników. Od tego czasu przeniósł się i wykonywał bardzo interesującą pracę nad chipsetami kalkulatorów w nowej firmie, którą założył w Valley Forge w Pensylwanii .

Paivinen założył firmę MOS Technology w 1969 roku wraz z dwoma innymi dyrektorami General Instrument, Mortem Jaffe i Donem McLaughlinem. Allen-Bradley , dostawca komponentów elektronicznych i sterowników przemysłowych, nabył większościowy udział w 1970 roku. Firma zaprojektowała i wyprodukowała niestandardowe układy scalone dla klientów oraz opracowała linię chipów kalkulatorów.

Po tym, jak wysiłki Mostka nie powiodły się, Peddle podszedł do Paivinena, który „od razu to dostał”. 19 sierpnia 1974 roku Chuck Peddle, Bill Mensch, Rod Orgill, Harry Bawcom, Ray Hirt, Terry Holdt i Wil Mathys opuścili Motorolę, by dołączyć do MOS. Mike Janes dołączył później. Z siedemnastu projektantów chipów i osób zajmujących się układami w zespole 6800, ośmiu zostało. Celem zespołu było zaprojektowanie i wyprodukowanie taniego mikroprocesora do aplikacji wbudowanych oraz dotarcie do jak najszerszej bazy klientów. Byłoby to możliwe tylko wtedy, gdyby mikroprocesor był tani, a zespół ustalił docelową cenę na poziomie 5 USD. Mensch stwierdził później, że celem nie była sama cena procesora, ale stworzenie zestawu chipów, który mógłby być sprzedawany po 20 USD, aby konkurować z niedawno wprowadzonym Intelem 4040, który był sprzedawany za 29 USD w podobnym kompletnym chipsecie.

Chipy są produkowane przez drukowanie wielu kopii projektu chipa na powierzchni „wafla” , cienkiego dysku z wysoce czystego krzemu. Mniejsze żetony mogą być drukowane w większej liczbie na tej samej płytce, co obniża ich względną cenę. Dodatkowo wafle zawsze zawierają pewną liczbę drobnych fizycznych defektów, które są rozsiane po powierzchni. Każdy chip wydrukowany w tym miejscu ulegnie uszkodzeniu i należy go wyrzucić. Mniejsze żetony oznaczają mniejsze prawdopodobieństwo wydrukowania pojedynczej kopii na defektu. Z obu tych powodów koszt produktu końcowego jest silnie uzależniony od rozmiaru konstrukcji chipa.

Pierwotne 6800 Kawałki miały być 180 x 180 milicali (4,6 x 4,6 mm) , ale układ zakończono w 212 x 212 milicali (5,4 x 5,4 mm) albo powierzchni 29,0 mm 2 . Dla nowego projektu, celem koszt zażądał cel wielkości 153 x 168 mil (3,9 x 4,3 mm) , lub o powierzchni 16,6 mm 2 . Do osiągnięcia tego celu potrzeba kilku nowych technik.

Przeprowadzka do NMOS

Na rynku pojawiły się dwa znaczące udoskonalenia, które pojawiły się w momencie projektowania 6502, które zapewniły znaczną redukcję kosztów. Pierwszym było przejście na NMOS z ładowaniem zubożonym . 6800 wykorzystywał wczesny proces NMOS, który wymagał trzech napięć zasilania, ale jedną z cech chipa był pokładowy podwajacz napięcia, który pozwalał na użycie pojedynczego zasilania +5 V dla +5, -5 i +12 wewnętrznie, w przeciwieństwie do innych układów era jak Intel 8080, która wymagała trzech oddzielnych pinów zasilających. Chociaż ta funkcja zmniejszyła złożoność zasilacza i układu pinów, nadal wymagała oddzielnych szyn zasilających do różnych bramek w chipie, zwiększając złożoność i rozmiar. Po przejściu na nowy projekt z ładowaniem zubożającym wystarczyło tylko jedno źródło zasilania +5, eliminując całą tę złożoność.

Kolejną praktyczną zaletą było to, że sygnał zegara dla wcześniejszych procesorów musiał być wystarczająco silny, aby wytrzymać wszelkie rozpraszanie podczas przechodzenia przez obwody, co prawie zawsze wymagało oddzielnego zewnętrznego układu scalonego, który mógłby dostarczyć wystarczająco silny sygnał. Dzięki obniżonym zapotrzebowaniu na energię NMOS zegar można przenieść na układ, upraszczając ogólną konstrukcję komputera. Zmiany te znacznie zmniejszyły złożoność i koszt wdrożenia kompletnego systemu.

Kolejną zmianą, jaka miała miejsce, było wprowadzenie maskowania projekcji. Wcześniej chipy były wzorowane na powierzchni wafla, umieszczając maskę na powierzchni wafla, a następnie oświetlając ją jasnym światłem. Maski często zbierały drobne kawałki brudu lub fotomaski, gdy były zdejmowane z chipa, powodując skazy w tych miejscach podczas późniejszego maskowania. Przy skomplikowanych konstrukcjach, takich jak procesory, zastosowanych byłoby 5 lub 6 takich etapów maskowania, a prawdopodobieństwo, że przynajmniej jeden z tych etapów wprowadzi wadę, było bardzo duże. W większości przypadków 90% takich projektów było wadliwych, co skutkowało 10% wydajnością. Cena przykładów roboczych musiała pokryć koszt produkcji 90%, które zostały wyrzucone.

W 1973 roku Perkin-Elmer wprowadził system Micralign , który wyświetlał obraz maski na wafelku zamiast wymagać bezpośredniego kontaktu. Maski nie zbierały już brudu z płytek i wytrzymywały mniej więcej 100 000 użyć niż 10. Wyeliminowało to błędy krok po kroku i wysokie wskaźniki defektów, które wcześniej występowały w złożonych projektach. Zyski na procesorach natychmiast podskoczyły z 10% do 60 lub 70%. Oznaczało to, że cena procesora spadła mniej więcej o tę samą kwotę, a mikroprocesor nagle stał się urządzeniem towarowym.

Istniejące linie produkcyjne MOS Technology były oparte na starszej technologii PMOS, ale nie rozpoczęły jeszcze pracy z NMOS, kiedy przybył zespół. Paivinen obiecał, że uruchomi linię NMOS na czas, aby rozpocząć produkcję nowego procesora. Dotrzymał obietnicy, nowa linia była gotowa do czerwca 1975 roku.

Uwagi dotyczące projektu

Chuck Peddle, Rod Orgill i Wil Mathys zaprojektowali początkową architekturę nowych procesorów. Artykuł w magazynie EDN z września 1975 r. przedstawia podsumowanie projektu:

Rodzina 650X MOS Technology to świadoma próba ośmiu byłych pracowników Motoroli, którzy pracowali nad rozwojem systemu 6800, aby wyprodukować część, która zastąpi i przewyższy 6800, ale będzie sprzedawać mniej. Korzystając z perspektywy czasu uzyskanej w projekcie 6800, zespół MOS Technology kierowany przez Chucka Peddle'a dokonał następujących zmian architektonicznych w procesorze Motorola…

Główną zmianą pod względem rozmiaru chipa była eliminacja sterowników trójstanowych z wyjść magistrali adresowej. Zostało to uwzględnione w 6800, aby umożliwić mu pracę z innymi układami w roli bezpośredniego dostępu do pamięci (DMA) i współprzetwarzania, kosztem znacznej przestrzeni na matrycy. W praktyce korzystanie z takiego systemu wymagało, aby inne urządzenia były podobnie złożone, a projektanci zamiast tego używali systemów off-chip do koordynowania takiego dostępu. 6502 po prostu usunął tę funkcję, zgodnie z jego konstrukcją jako niedrogiego kontrolera używanego do określonych zadań i komunikowania się z prostymi urządzeniami. Peddle zasugerował, że każdy, kto rzeczywiście wymaga tego stylu dostępu, może go zaimplementować za pomocą jednego 74158 .

Kolejną istotną różnicą było uproszczenie rejestrów. Na początek jeden z dwóch akumulatorów został usunięty. Rejestry ogólnego przeznaczenia, takie jak akumulatory, muszą być dostępne dla wielu części dekodera rozkazów, a zatem wymagają znacznej ilości okablowania w celu przeniesienia danych do iz miejsca ich przechowywania. Dwa akumulatory ułatwiają wiele zadań związanych z kodowaniem, ale kosztują samą konstrukcję chipa znaczną złożonością. Dalsze oszczędności poczyniono poprzez zmniejszenie rejestru stosu z 16 do 8 bitów, co oznacza, że stos mógł mieć tylko 256 bajtów, co wystarczało do jego zamierzonej roli jako mikrokontrolera.

16-bitowy rejestr indeksowy IX został podzielony na dwie części, stając się X i Y. Co ważniejsze, zmienił się styl dostępu; w 6800, IX posiadał 16-bitowy adres, który został przesunięty o liczbę dostarczoną z instrukcją, oba zostały dodane, aby uzyskać ostateczny adres. W 6502 (i większości innych projektów) adres bazowy był przechowywany w instrukcji, a X lub Y zostały do niego dodane.

Ostatecznie zestaw instrukcji został uproszczony, zwalniając miejsce w dekoderze i logice sterowania. Z oryginalnych 72 instrukcji w 6800 pozostało 56. Wśród usuniętych były wszelkie instrukcje, które przenosiły dane między dwoma akumulatorami 6800, a także szereg instrukcji rozgałęzień inspirowanych przez PDP-11, takich jak możliwość bezpośredniego porównania dwóch wartości numerycznych. 6502 używał prostszego systemu, który obsługiwał porównania, wykonując obliczenia matematyczne na akumulatorze, a następnie sprawdzając flagi wyników.

Wysokopoziomowy projekt układu musiał zostać przekształcony w rysunki tranzystorów i interkonektów. W MOS Technology „układ” był bardzo ręcznym procesem wykonywanym za pomocą kolorowych ołówków i papieru welinowego. Układ składał się z tysięcy kształtów wielokątów na sześciu różnych rysunkach; po jednym na każdą warstwę procesu produkcyjnego. Biorąc pod uwagę ograniczenia rozmiaru, cały projekt chipa musiał być stale przemyślany. Mensch i Paivinen pracowali nad dekoderem instrukcji, podczas gdy Mensch, Peddle i Orgill pracowali nad ALU i rejestrami. Dalszym postępem, opracowanym na imprezie, był sposób na współdzielenie części okablowania wewnętrznego, aby umożliwić zmniejszenie rozmiaru jednostki ALU.

Pomimo ich najlepszych starań, ostateczny projekt okazał się o 5 mil za szeroki. Pierwsze 6502 wióry są 168 x 183 milicali (4,3 x 4,7 mm) , i obszar 19,8 mm 2 . Instrukcja obrotu w prawo (ROR) nie działała w pierwszym krzemie, więc instrukcja została chwilowo pominięta w publikowanych dokumentach, ale kolejna iteracja projektu skurczyła układ i poprawiła instrukcję obrotu w prawo, która została następnie włączona do poprawionej dokumentacji .

Przedstawiamy 6501 i 6502

MOS wprowadziłby dwa mikroprocesory oparte na tej samej konstrukcji: 6501 podłączałby się do tego samego gniazda co Motorola 6800, podczas gdy 6502 zmienił układ pinów, aby obsługiwać wbudowany oscylator zegarowy. Obydwa współpracowałyby z innymi układami pomocniczymi zaprojektowanymi dla 6800. Nie uruchamiałyby oprogramowania 6800, ponieważ miały inny zestaw instrukcji, różne rejestry i przeważnie różne tryby adresowania. Rod Orgill był odpowiedzialny za projekt 6501; asystował Johnowi Buchananowi w Motoroli na 6800. Bill Mensch zrobił 6502; był projektantem 6820 Peripheral Interface Adapter (PIA) w Motoroli. Harry Bawcom, Mike Janes i Sydney-Anne Holt pomogli w aranżacji.

Wprowadzenie mikroprocesora MOS Technology różniło się od tradycyjnego, wielomiesięcznego wprowadzenia produktu na rynek. Pierwsze uruchomienie nowego układu scalonego jest zwykle wykorzystywane do testów wewnętrznych i udostępniane wybranym klientom jako „próbki inżynieryjne”. Te chipy często mają drobne defekty projektowe, które zostaną poprawione przed rozpoczęciem produkcji. Celem Chuck Peddle było sprzedanie pierwszej serii chipów 6501 i 6502 uczestnikom targów Wescon w San Francisco, które rozpoczęły się 16 września 1975 roku. Peddle był bardzo skutecznym rzecznikiem, a mikroprocesory MOS Technology były szeroko omawiane w prasie branżowej. Jedną z pierwszych była całostronicowa historia o mikroprocesorach MCS6501 i MCS6502 w magazynie Electronics z 24 lipca 1975 roku . Artykuły ukazały się również w EE Times (24 sierpnia 1975), EDN (20 września 1975), Electronic News (3 listopada 1975), Byte (listopad 1975) i Microcomputer Digest (listopad 1975). Reklamy modelu 6501 pojawiły się w kilku publikacjach w pierwszym tygodniu sierpnia 1975 roku. Model 6501 można było kupić w Wescon za 20 dolarów za sztukę. We wrześniu 1975 r. w reklamach znalazły się zarówno mikroprocesory 6501, jak i 6502. 6502 kosztowałby tylko 25 USD (równowartość 120 USD w 2020 r.).

Kiedy MOS Technology przybył do Wescon, okazało się, że wystawcom nie wolno sprzedawać niczego na parkiecie. Wynajęli apartament MacArthur Suite w hotelu St. Francis i skierowali tam klientów do zakupu procesorów. W apartamencie procesory były przechowywane w dużych słojach, aby sugerować, że frytki są w produkcji i są łatwo dostępne. Klienci nie wiedzieli, że dolna połowa każdego słoika zawiera niefunkcjonalne chipsy. Żetony kosztowały 20 USD i 25 USD, podczas gdy pakiet dokumentacji to dodatkowe 10 USD. Zachęcano użytkowników do robienia kserokopii dokumentów, co jest niedrogim sposobem dystrybucji informacji o produkcie przez technologię MOS. Wstępne arkusze danych zawierały tylko 55 instrukcji, z wyjątkiem instrukcji Rotate Right (ROR), która nie działała poprawnie na tych wczesnych chipach. Recenzje w Byte i EDN odnotowały brak instrukcji ROR. Kolejna zmiana układu naprawiła ten problem, a arkusz danych z maja 1976 r. zawierał 56 instrukcji. Peddle chciał, aby każdy zainteresowany inżynier i hobbysta miał dostęp do chipów i dokumentacji; inne firmy półprzewodnikowe chciały zajmować się tylko „poważnymi” klientami. Na przykład firma Signetics wprowadzała mikroprocesor 2650 , a w swoich reklamach zachęcała czytelników do pisania w celu uzyskania informacji na papierze firmowym ich firmy.

| Szpilka | 6800 | 6501 | 6502 |

|---|---|---|---|

| 2 | Postój | Gotowy | Gotowy |

| 3 | ∅1 (w) | ∅1 (w) | ∅1 (na zewnątrz) |

| 5 | Prawidłowy adres pamięci | Prawidłowy adres pamięci | NC |

| 7 | Dostępny autobus | Dostępny autobus | SYNCHRONIZACJA |

| 36 | Włączenie magistrali danych | Włączenie magistrali danych | NC |

| 37 | ∅2 (w) | ∅2 (w) | ∅0 (w) |

| 38 | NC | NC | Ustaw flagę przepełnienia |

| 39 | Kontrola trójstanowa | NC | ∅2 (na zewnątrz) |

Pozew Motoroli

Wprowadzenie modelu 6501/6502 do druku i na targach Wescon było ogromnym sukcesem. Minusem było to, że uwagę Motoroli przyciągnęły obszerne relacje prasowe. W październiku 1975 r. Motorola obniżyła cenę pojedynczego mikroprocesora 6800 z 175 USD do 69 USD. Zestaw do projektowania systemu za 300 USD został obniżony do 150 USD, a teraz był wyposażony w płytkę drukowaną. 3 listopada 1975 r. Motorola wystąpiła do sądu federalnego o wydanie nakazu zakazującego produkcji i sprzedaży produktów mikroprocesorowych przez technologię MOS. Złożyli również pozew o naruszenie patentów i przywłaszczenie tajemnic handlowych. Motorola twierdziła, że siedmiu byłych pracowników dołączyło do MOS Technology, aby stworzyć produkty mikroprocesorowe tej firmy.

Motorola była miliardową firmą z prawdopodobną sprawą i prawnikami. 30 października 1974 roku Motorola złożyła liczne wnioski patentowe dotyczące rodziny mikroprocesorów i otrzymała dwadzieścia pięć patentów. Pierwszym był czerwiec 1976, a drugim Bill Mensch 6 lipca 1976, za układ chipów 6820 PIA. Patenty te obejmowały magistralę 6800 i sposób, w jaki chipy peryferyjne komunikowały się z mikroprocesorem. Motorola rozpoczęła produkcję tranzystorów w 1950 roku i posiadała portfolio patentów na półprzewodniki. Allen-Bradley postanowił nie walczyć z tą sprawą i odsprzedał swoje zainteresowanie technologią MOS założycielom. W garniturze wymieniono czterech byłych inżynierów Motoroli: Chuck Peddle, Will Mathys, Bill Mensch i Rod Orgill. Wszyscy zostali nazwani wynalazcami w 6800 zgłoszeniach patentowych. Podczas procesu odkrywania Motorola odkryła, że jeden inżynier, Mike Janes, zignorował instrukcje Peddle'a i przekazał swoje dokumenty projektowe 6800 do firmy MOS Technology. W marcu 1976 roku niezależna obecnie technologia MOS kończyła się i musiała załatwić sprawę. Zgodzili się zrezygnować z procesora 6501, zapłacić Motoroli 200 000 dolarów i zwrócić dokumenty, które według Motoroli były poufne. Obie firmy zgodziły się na krzyżową licencję na patenty na mikroprocesory. W maju Motorola obniżyła cenę pojedynczego mikroprocesora 6800 do 35 USD. Do listopada Commodore przejęło technologię MOS.

Komputery i gry

Mając za sobą problemy prawne, MOS nadal miał problem z nakłonieniem programistów do wypróbowania swojego procesora, co skłoniło Chucka Peddle'a do zaprojektowania komputera jednopłytkowego MDT-650 ("microcomputer development terminal") . Inna grupa wewnątrz firmy zaprojektowała KIM-1 , który był sprzedawany jako półkompletny i mógł zostać przekształcony w użyteczny system po dodaniu terminala komputerowego innej firmy i kompaktowego napędu kasetowego . Ku ich zdumieniu KIM-1 dobrze sprzedawał się hobbystom i majsterkowiczom, a także inżynierom, do których był skierowany. Powiązany system sterowania/szkolenia/rozwoju Rockwell AIM 65 również wypadł dobrze. Oprogramowanie w AIM 65 zostało oparte na oprogramowaniu MDT. Innym mniej więcej podobnym produktem był Synertek SYM-1 .

Jednym z pierwszych „publicznych” zastosowań tego projektu był mikrokomputer Apple I , wprowadzony w 1976 roku. 6502 został następnie użyty w Commodore PET i Apple II , oba wydane w 1977 roku. Później był używany w 8-bitowym Atari rodzina i Acorn Atom komputery domu, BBC Micro , Commodore VIC-20 i inne projekty zarówno dla komputerów domowych i biznesowych, takich jak Ohio Scientific i ORIC . 6510 , bezpośredni następca 6502 w cyfrowy port We / Wy i tri-state adresowej autobusem, był CPU wykorzystany w bestsellerowej Commodore 64 domowym komputerze. 6520 i / lub 6502-variant procesory były używane we wszystkich Commodore dyskietce napędów dla wszystkich swoich komputerów 8-bitowych, z linii PET (z których część miała dwa procesory 6502-based) przez Commodore 128, w tym Commodore 64 , a także we wszystkich napędach dyskowych Atari dla całej ich linii komputerów 8-bitowych, od 400/800 do XEGS.

Innym ważnym zastosowaniem rodziny 6500 były gry wideo. Pierwszym, który wykorzystał konstrukcję procesora, był Atari VCS, później przemianowany na Atari 2600 . VCS używał wariantu 6502 o nazwie 6507 , który miał mniej pinów i w rezultacie mógł adresować tylko 8 KB pamięci. Sprzedano by miliony konsol Atari, każda z procesorem MOS. Innym znaczącym zastosowaniem było Nintendo Entertainment System i Famicom . 6502 używany w NES był drugą wersją źródłową Ricoh , częściowym systemem na chipie , który nie miał trybu dziesiętnego kodowanego binarnie , ale dodał 22 rejestry mapowane w pamięci i sprzęt do generowania dźwięku, odczyt na joysticku i lista sprite DMA . Nazywany 2A03 w konsolach NTSC i 2A07 w konsolach PAL (różnica polega na współczynniku dzielnika pamięci i tabeli wyszukiwania częstotliwości próbkowania dźwięku), ten procesor został wyprodukowany wyłącznie dla Nintendo . Atari Lynx W wersji 4 MHz na wióra 65SC02 .

W latach 80. popularny magazyn elektroniczny Elektor/Elektuur użył procesora w swojej mikroprocesorowej płytce rozwojowej Junior Computer .

- Komputery domowe i konsole do gier wideo korzystające z 6502 lub jego wariantów

Opis techniczny

| 1 5 | 1 4 | 1 3 | 1 2 | 1 1 | 1 0 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | (pozycja bitowa) |

| Główne rejestry | ||||||||||||||||

| A | ccumulator | |||||||||||||||

| Rejestry indeksowe | ||||||||||||||||

| x | Indeks X | |||||||||||||||

| Tak | Indeks Y | |||||||||||||||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | S | S przyczepność wskaźnik | |||||||

| Licznik programu | ||||||||||||||||

| PC | P ROGRAM C ounter | |||||||||||||||

| Rejestr statusu | ||||||||||||||||

| n | V | - | b | D | i | Z | C | P rocessor F opóźnienia | ||||||||

6502 to 8-bitowy procesor little-endian z 16-bitową szyną adresową . Pierwotne wersje wytwarzano stosując 8 um procesu technologicznego elementu z dyszy wielkości od 3,9 mm x 4,3 mm (reklamowanego jako 153 milicali × 168 milicali ), do powierzchni całkowitej 16,6 mm 2 .

Wewnętrzna logika działa z taką samą szybkością jak zegar zewnętrzny, ale pomimo niskich częstotliwości taktowania (zwykle w okolicach 1 do 2 MHz ), wydajność 6502 była konkurencyjna w porównaniu z innymi współczesnymi procesorami używającymi znacznie szybszych zegarów. Wynika to częściowo z prostego automatu stanów zaimplementowanego przez logikę kombinacyjną (bezzegarową) w większym stopniu niż w wielu innych konstrukcjach; zegar dwufazowy (zapewniający dwie synchronizacje na cykl) mógłby w ten sposób bezpośrednio sterować cyklem maszyny. Typowe instrukcje mogą zająć o połowę mniej cykli na 6502 niż na współczesnych projektach. Podobnie jak większość prostych procesorów tamtych czasów, dynamiczny układ NMOS 6502 nie jest sekwencjonowany przez ROM z mikrokodem, ale wykorzystuje PLA (który zajmuje około 15% powierzchni układu) do dekodowania i sekwencjonowania instrukcji. Podobnie jak w większości 8-bitowych mikroprocesorów, chip wykonuje pewne ograniczone nakładanie się pobierania i wykonywania.

Niska częstotliwość taktowania łagodziła wymagania dotyczące szybkości pamięci i urządzeń peryferyjnych podłączonych do procesora, ponieważ tylko około 50% cyklu zegara było dostępne dla dostępu do pamięci (ze względu na konstrukcję asynchroniczną ta część była bardzo zróżnicowana w zależności od wersji układu). Było to krytyczne w czasach, gdy przystępna cenowo pamięć miała czasy dostępu w zakresie 250–450 ns .

Ponieważ chip uzyskiwał dostęp do pamięci tylko podczas pewnych części cyklu zegara, a te cykle były wskazywane przez pin PHI2 o niskim taktowaniu, inne chipy w systemie mogły uzyskać dostęp do pamięci w czasie, gdy 6502 był poza szyną. Czasami nazywano to „ukrytym dostępem”. Ta technika była szeroko stosowana w systemach komputerowych; używaliby pamięci zdolnej do dostępu z częstotliwością 2 MHz, a następnie uruchamialiby procesor z częstotliwością 1 MHz. Gwarantowało to, że procesor i sprzęt wideo mogą przeplatać swoje dostępy, z całkowitą wydajnością odpowiadającą wydajności urządzenia pamięci. Kiedy w latach 80. pojawiły się szybsze pamięci, nowsze maszyny mogły działać z wyższymi częstotliwościami taktowania, jak procesor 2 MHz w BBC Micro i nadal korzystać z technik współdzielenia magistrali.

Rejestry

Podobnie jak jego poprzednik, 6800, 6502 ma bardzo mało rejestrów . Rejestry 6502 zawierają jeden 8-bitowy rejestr akumulacyjny (A), dwa 8-bitowe rejestry indeksowe (X i Y), 7 1-bitowych bitów flagi stanu procesora (P) – konkretnie od bitu 7 do bitu 0 w P są to ujemny (N), przepełnienie (V), zarezerwowany , przerwa (B), dziesiętny (D), przerwanie przerwania (I), zero (Z) i flaga przeniesienia (C) – 8-bitowy wskaźnik stosu (S), oraz 16-bitowy licznik programu (PC). Można to porównać do typowego projektu z tej samej epoki, Z80 , który ma osiem 8-bitowych rejestrów ogólnego przeznaczenia, które można połączyć w cztery 16-bitowe. Z80 miał również kompletny zestaw alternatywnych rejestrów, które tworzyły w sumie szesnaście rejestrów ogólnego przeznaczenia.

Aby nieco zrekompensować brak rejestrów, 6502 zawierał tryb adresowania strony zerowej , który wykorzystuje jeden bajt adresu w instrukcji zamiast dwóch potrzebnych do zaadresowania pełnych 64 KB pamięci. Zapewnia to szybki dostęp do pierwszych 256 bajtów pamięci RAM przy użyciu krótszych instrukcji. Chuck Peddle powiedział w wywiadach, że konkretną intencją było umożliwienie wykorzystania tych pierwszych 256 bajtów pamięci RAM jako rejestrów.

Przestrzeń adresowa stosu jest połączona na stałe ze stroną pamięci $01 , tj. zakresem adresów $0100 – $01FF ( 256 – 511 ). Dostęp programowy do stosu odbywa się za pomocą czterech domyślnych instrukcji trybu adresowania, których funkcją jest wypychanie lub wysuwanie (wyciąganie) akumulatora lub rejestru stanu procesora. Ten sam stos jest również używany do wywołań podprogramów za pośrednictwem instrukcji JSR (skok do podprogramu) i RTS (powrót z podprogramu) oraz do obsługi przerwań .

Adresowanie

Układ efektywnie wykorzystuje rejestry indeksu i stosu z kilkoma trybami adresowania , w tym szybkim trybem „strony bezpośredniej” lub „strony zerowej”, podobnym do tego, który znajduje się na PDP-8 , który uzyskuje dostęp do lokalizacji pamięci od adresów od 0 do 255 za pomocą jednego Adres 8-bitowy (zapisując cykl normalnie wymagany do pobrania bajtu wyższego rzędu adresu) – kod dla 6502 używa strony zerowej, podobnie jak kod dla innych procesorów używałby rejestrów. Na niektórych mikrokomputerach opartych na 6502 z systemem operacyjnym, system operacyjny wykorzystuje większość strony zerowej, pozostawiając użytkownikowi tylko kilka lokalizacji.

Tryby adresowania obejmują również niejawne (1-bajtowe instrukcje); bezwzględny (3 bajty); indeksowany bezwzględny (3 bajty); indeksowana strona zero (2 bajty); względne (2 bajty); akumulator (1); pośrednie,x i pośrednie,y (2); i natychmiastowe (2). Tryb bezwzględny jest trybem ogólnego przeznaczenia. Instrukcje rozgałęzienia używają podpisanego 8-bitowego przesunięcia względem instrukcji po rozgałęzieniu; zakres liczbowy -128..127 przekłada się zatem na 128 bajtów wstecz i 127 bajtów do przodu od instrukcji następującej po rozgałęzieniu (co oznacza 126 bajtów wstecz i 129 bajtów do przodu od początku instrukcji rozgałęzienia). Tryb akumulatora wykorzystuje akumulator jako efektywny adres i nie wymaga żadnych danych operandowych . Tryb natychmiastowy używa 8-bitowego operandu literału .

Adresowanie pośrednie

Tryby pośrednie są przydatne do przetwarzania tablic i innych pętli. W trybie 5/6 cyklu "(pośredni), y", 8-bitowy rejestr Y jest dodawany do 16-bitowego adresu bazowego odczytanego ze strony zerowej, który znajduje się za jednym bajtem po opcodzie. Rejestr Y jest zatem rejestrem indeksowym w tym sensie, że jest używany do przechowywania rzeczywistego indeksu (w przeciwieństwie do rejestru X w 6800, gdzie adres bazowy był bezpośrednio przechowywany i do którego można było dodać natychmiastowe przesunięcie). Zwiększanie rejestru indeksu w celu przejścia po tablicy bajtów zajmuje tylko dwa dodatkowe cykle. W rzadziej używanym trybie "(indirect,x)" efektywny adres operacji znajduje się pod adresem strony zerowej utworzonym przez dodanie drugiego bajtu instrukcji do zawartości rejestru X. Używając trybów indeksowanych, strona zerowa skutecznie działa jako zestaw do 128 dodatkowych (choć bardzo powolnych) rejestrów adresowych.

6502 może wykonywać dodawanie i odejmowanie w postaci dwójkowej lub dziesiętnej kodowanej binarnie . Umieszczenie procesora w trybie BCD za pomocą instrukcji SED(set D flag) powoduje arytmetykę dziesiętną, w $99 + $01wyniku której zostanie ustawiony $00 i flaga przeniesienia (C). W trybie binarnym ( CLD, flaga kasowania D), ta sama operacja spowodowałaby wyczyszczenie 9A $ i flagi przeniesienia. Poza Atari BASIC tryb BCD był rzadko używany w aplikacjach domowych.

Zobacz Witaj świecie! artykuł zawierający prosty ale charakterystyczny przykład asemblera 6502 .

Instrukcje i kody operacyjne

Kody operacyjne instrukcji 6502 ( kody operacyjne ) mają długość ośmiu bitów i mają ogólną postać AAABBBCC, gdzie AAA i CC definiują kod operacyjny, a BBB określa tryb adresowania.

Rozważmy na przykład ORAinstrukcję, która wykonuje bitowe OR na bitach w akumulatorze z inną wartością. Opcode instrukcji ma postać 000bbb01, gdzie bbb może być 010 dla wartości trybu natychmiastowego (stałej), 001 dla adresu stałego strony zerowej, 011 dla adresu bezwzględnego i tak dalej.

Ten wzorzec nie jest absolutny i istnieje szereg wyjątków. Jednak tam, gdzie ma to zastosowanie, pozwala łatwo zdekonstruować wartości opcode z powrotem do mnemoniki asemblera dla większości instrukcji, obsługując przypadki brzegowe za pomocą kodu specjalnego przeznaczenia.

Spośród 256 możliwych opkodów dostępnych przy użyciu 8-bitowego wzorca, oryginalny 6502 używa 151 z nich, zorganizowanych w 56 instrukcji z (prawdopodobnie) wieloma trybami adresowania . W zależności od instrukcji i trybu adresowania, kod operacji może wymagać zera, jednego lub dwóch dodatkowych bajtów na operandy. Stąd 6502 instrukcje maszynowe różnią się długością od jednego do trzech bajtów. Operand jest przechowywany w typowym dla 6502 formacie little-endian .

65c816 , 16-bitowy CMOS potomkiem 6502 wspiera również adresowanie 24-bitowe, co prowadzi do instrukcji jest zmontowany z trzech bajtów argumentu operacji, również ułożonych w formacie ostrokońcej.

Pozostałe 105 kodów operacyjnych jest niezdefiniowanych. W pierwotnym projekcie instrukcje, w których 4-bity niskiego rzędu ( nibble ) były 3, 7, B lub F, nie były używane, co zapewniało miejsce na przyszłą rozbudowę. Podobnie kolumna $2x miała tylko jeden wpis, . Rozdano pozostałe 25 pustych miejsc. Niektóre z pustych gniazd zostały wykorzystane w 65C02, aby zapewnić zarówno nowe instrukcje, jak i wariacje istniejących z nowymi trybami adresowania. Instrukcje $Fx początkowo pozostawiono za darmo, aby umożliwić zewnętrznym dostawcom dodawanie własnych instrukcji, ale późniejsze wersje 65C02 ustandaryzowały zestaw instrukcji do manipulowania bitami opracowanymi przez Rockwell Semiconductor .

LDX #constant

język programowania

Instrukcja języka asemblerowego 6502 składa się z trzyznakowej instrukcji mnemonicznej , po której następują dowolne operandy . Instrukcje, które nie przyjmują oddzielnego operandu, ale celują w pojedynczy rejestr w oparciu o tryb adresowania, łączą rejestr docelowy w mnemoniku instrukcji, więc asembler używa INXw przeciwieństwie INC Xdo zwiększania rejestru X.

Tabela instrukcji

| Macierz opcode dla zestawu instrukcji 6502 | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Tryby adresowania: A – akumulator, # – natychmiastowy, zpg – strona zerowa, abs – bezwzględna, ind – pośrednia, X – indeksowana rejestrem X, Y – indeksowana rejestrem Y, rel – względna | ||||||||||||

| Wysoka skubać | Niskie skubanie | |||||||||||

| 0 | 1 | 2 | 4 | 5 | 6 | 8 | 9 | A | C | D | mi | |

| 0 | BRK | ORA ( ind ,X) | ORA zpg | ASL ZPG | PHP | ORA # | ASL A | ORA abs | ASL abs | |||

| 1 | BPL rel | ORA ( ind ), Y | ORA zpg ,X | ASL zip ,X | WŻCh | ORA abs ,Y | ORA abs ,X | ASL abs ,X | ||||

| 2 | JSR abs | ORAZ ( ind ,X) | BIT ZPG | ORAZ zpg | ROL zpg | PLP | ORAZ # | ROL A | BIT abs | ORAZ abs | ROL abs | |

| 3 | Względne BMI | I ( ind ),Y | ORAZ zip ,X | ROL zpg ,X | SEC | I abs ,Y | I abs ,X | ROL abs ,X | ||||

| 4 | RTI | EOR ( ind ,X) | EOR ZPG | Plik LSR | PHA | EOR # | LSR A | JMP abs | EOR abs | LSR abs | ||

| 5 | BVC rel | EOR ( ind ),Y | EOR zpg ,X | LSR zip ,X | CLI | EOR abs ,Y | EOR abs ,X | LSR abs ,X | ||||

| 6 | RTS | ADC ( ind ,X) | ADC ZPG | ROR zpg | PLA | ADC # | ROR A | JMP ( ind ) | ADC abs | ROR abs | ||

| 7 | BVS rel | ADC ( ind ), Y | ADC zip ,X | ROR zpg ,X | SEI | ADC abs ,Y | ADC abs ,X | ROR abs ,X | ||||

| 8 | STA ( ind ,X) | STY ZPG | STA ZPG | Plik STX | DEY | TXA | STY abs | STA abs | STX abs | |||

| 9 | BCC rel | STA ( ind ), Y | STY zip ,X | STA zpg ,X | STX s.pg ,Y | TYA | STA abs ,Y | TXS | STA abs ,X | |||

| A | LDY # | LDA ( ind ,X) | LDX # | LDY zpg | Kodowanie LDA | LDX zip | TAY | LDA # | PODATEK | LDY abs | LDA abs | LDX abs |

| b | BCS rel | LDA ( ind ), Y | LDY zip ,X | LDA zip ,X | LDX skompresowany ,Y | CLV | LDA abs ,Y | TSX | LDY abs ,X | LDA abs ,X | LDX abs ,Y | |

| C | CPY # | CMP ( ind ,X) | CPY zpg | CMP ZPG | DEC zpg | INY | CMP # | DEX | CPY abs | CMP abs | DEC abs | |

| D | BNE rel | CMP ( ind ), Y | CMP zpg ,X | DEC zpg ,X | CLD | CMP abs ,Y | CMP abs ,X | DEC abs ,X | ||||

| mi | CPX # | SBC ( ind ,X) | CPX ZPG | SBC ZPG | INC ZPG | INX | SBC # | NOP | CPX abs | SBC abs | INC abs | |

| F | BEQ rel | SBC ( ind ), Y | SBC zip ,X | INC zpg ,X | SED | SBC abs ,Y | SBC abs ,X | INC abs ,X | ||||

| Puste kody operacji (np. F2 ) i wszystkie kody operacji, których małe półbajty to 3 , 7 , B i F są niezdefiniowane w zestawie instrukcji 6502. | ||||||||||||

Szczegółowe zachowanie

Wejście przerwania niemaskowanego (NMI) procesora jest wrażliwe na zbocze , co oznacza, że przerwanie jest wyzwalane przez opadające zbocze sygnału, a nie jego poziom. Implikacją tej funkcji jest to, że obwód przerwania przewodowego OR nie jest łatwo obsługiwany. Jednak zapobiega to również występowaniu zagnieżdżonych przerwań NMI, dopóki sprzęt nie sprawi, że wejście NMI ponownie stanie się nieaktywne, często pod kontrolą obsługi przerwań NMI .

Jednoczesne zapewnienie linii przerwań sprzętowych NMI i IRQ (maskowalnych) powoduje, że IRQ jest ignorowane. Jednakże, jeśli linia IRQ pozostaje zapewniona po obsłudze NMI, procesor natychmiast zareaguje na IRQ, ponieważ IRQ jest wrażliwe na poziom . W ten sposób w projekcie 6502 ustanowiono rodzaj wbudowanego priorytetu przerwań.

Flaga B jest ustawiana przez urządzenie 6502 okresowo próbkujące wyjście detektora krawędzi NMI i wejście IRQ. Sygnał IRQ o niskim poziomie jest rozpoznawany tylko wtedy, gdy IRQ są dozwolone przez flagę I. Jeżeli w ten sposób zostanie wykryte żądanie NMI lub (maskowalne) IRQ, flaga B jest ustawiana na zero i powoduje, że procesor wykonuje następną instrukcję BRK zamiast wykonywania następnej instrukcji na podstawie licznika programu.

Instrukcja BRK następnie odkłada status procesora na stos, z bitem flagi B ustawionym na zero. Pod koniec swojego wykonania instrukcja BRK resetuje wartość flagi B na jeden. Tylko w ten sposób można zmodyfikować flagę B. Jeśli instrukcja inna niż instrukcja BRK umieszcza flagę B na stosie jako część statusu procesora, flaga B ma zawsze wartość jeden.

Zbocze od niskiego do wysokiego na wejściu SO ustawia bit stanu przepełnienia procesora. Może to służyć do szybkiego reagowania na sprzęt zewnętrzny. Na przykład, szybki sterownik urządzenia odpytującego może odpytywać sprzęt tylko raz na trzy cykle za pomocą BVCinstrukcji rozgałęzienia rozgałęzienia na przepełnienie ( ), która rozgałęzia się do siebie, aż przepełnienie zostanie ustawione przez zbocze narastające SO. Commodore 1541 i inne Commodore dyskietki dyski użyć tej metody do wykrywania kiedy serializer jest gotowy do przeniesienia kolejny bajt danych dyskowych. Projekt sprzętu i oprogramowania systemu musi zapewniać, że SO nie wystąpi podczas przetwarzania arytmetycznego i obliczeń zakłócających.

Wariacje i pochodne

Istniało wiele wariantów oryginalnego NMOS 6502.

| Spółka | Model | Opis |

|---|---|---|

| 6502A | Chip 1,5 MHz w Asteroids Deluxe . | |

| 6502B | Wersja 6502 zdolna do pracy z maksymalną prędkością 2 MHz zamiast 1. B była używana w Apple III , BBC Micro i taktowanych 1,79 MHz, wczesnych 8-bitowych komputerach Atari . | |

| 6502C | „Oficjalny” 6502C był wersją oryginalnego 6502 zdolną do pracy z częstotliwością do 4 MHz.

Nie mylić z SALLY, customem 6502 zaprojektowanym dla Atari (czasem określanym przez nich jako „6502C”) ani z podobnie nazwanym 65C02 . |

|

| SALLY / C014806 / "6502C" |

Niestandardowe 6502 wariant przeznaczony dla Atari, stosowany w nowszych komputerach 8-bitowych Atari jak i Atari 5200 i Atari 7800 konsolach.

Zawiera sygnał HALT na pinie 35 i sygnał R/W na pinie 36 (te piny nie są połączone (N/C) w standardowym 6502). Pociągnięcie HALT do dołu powoduje przytrzaśnięcie zegara, wstrzymując procesor. Zostało to wykorzystane, aby umożliwić bezpośredni dostęp do pamięci obwodów wideo (DMA). Chociaż czasami w dokumentacji Atari jest określany jako „6502C”, nie jest to to samo, co „oficjalny” 6502C, a sam układ nigdy nie jest tak oznaczony. |

|

| Technologia MOS | 6503 | Zredukowane możliwości adresowania pamięci (4 KB) i brak wejścia RDY, w 28-pinowej obudowie DIP (z pominięciem fazy 1 (OUT), SYNC, redundantnych pinów Vss i SO w 6502). |

| Technologia MOS | 6504 | Zredukowana zdolność adresowania pamięci (8 KB), brak NMI i brak wejścia RDY, w 28-pinowej obudowie DIP (z pominięciem fazy 1 (OUT), SYNC, redundantnych pinów Vss i SO w 6502). |

| Technologia MOS | 6505 | Zredukowane możliwości adresowania pamięci (4 KB) i brak NMI, w 28-pinowej obudowie DIP (z pominięciem fazy 1 (OUT), SYNC, redundantnych pinów Vss i SO w 6502). |

| Technologia MOS | 6506 | Zredukowane możliwości adresowania pamięci (4 KB), brak NMI i brak wejścia RDY, ale wszystkie 3 piny zegara 6502 (tj. zegar wyjścia 2-fazowego), w 28-pinowej obudowie DIP (z SYNC, redundantnym Vss, i piny SO 6502 również pominięte). |

| Technologia MOS | 6507 | Zredukowana zdolność adresowania pamięci (8 KB) i brak przerwań, w 28-pinowym pakiecie DIP (z pominięciem fazy 1 (OUT), SYNC, redundantnych pinów Vss i SO w 6502). Ten chip był używany w systemie gier wideo Atari 2600 . |

| Technologia MOS | 6508 | Posiada wbudowany 8-bitowy port wejścia/wyjścia i 256 bajtów wewnętrznej statycznej pamięci RAM. |

| Technologia MOS | 6509 | Może adresować do 1 MB pamięci RAM jako 16 banków po 64 KB i był używany w serii Commodore CBM-II . |

| Technologia MOS | 6510 | Posiada wbudowany 6-bitowy programowalny port wejścia/wyjścia i był używany w Commodore 64 . 8500 jest faktycznie wersją HMOS 6510 i zastąpił ją w późniejszych wersjach C64. |

| Technologia MOS |

6512 6513 6514 6515 |

Technologia MOS 6512, 6513, 6514 i 6515 opiera się na zewnętrznym zegarze, zamiast używać wewnętrznego generatora zegara, takiego jak 650x (np. 6502). Wykorzystano to w niektórych projektach, w których zegary mogły działać asymetrycznie, zwiększając ogólną wydajność procesora.

6512 to 6502 z 2-fazowym wejściem zegarowym dla zewnętrznego oscylatora zegarowego, zamiast wbudowanego oscylatora zegarowego. 6513, 6514 i 6515 są podobnie równoważne (odpowiednio) 6503, 6504 i 6505 z tym samym dwufazowym wejściem zegarowym. 6512 był używany w BBC Micro B+64 . |

| Ricoh | 2A03 | Wariant 6502 zawierający procesor dźwięku i pozbawiony trybu BCD, stosowany w Nintendo Entertainment System . |

| Technologia MOS |

6591 6592 |

Projekty układów na chipie, które wykorzystują kompletne Atari 2600 w 48-pinowej obudowie DIP. |

| WDC | 65C02 |

Wersja CMOS NMOS 6502 zaprojektowana przez Billa Menscha z Western Design Center (WDC), charakteryzująca się zmniejszonym zużyciem energii, obsługą znacznie wyższych częstotliwości zegara, nowymi instrukcjami, nowymi trybami adresowania niektórych istniejących instrukcji oraz korektą erraty NMOS, takich jak JMP ($xxFF)błąd.

|

| WDC | 65SC02 | Wariant WDC 65C02 bez operacji manipulacji pojedynczymi bitami (RMB, SMB, BBR i BBS). Ten rdzeń, działający z częstotliwością 4 MHz, był używany w głównym układzie scalonym systemu Atari Lynx . |

| CSG (technologia MOS) | 65CE02 | Pochodna CMOS opracowana przez Commodore Semiconductor Group (CSG), dawniej MOS Technology. |

| Rockwella | R6511Q R6500/11, R6500/12, R6500/15 " Mikrokomputery jednoukładowe " |

Ulepszone wersje procesora opartego na 6502, obejmujące również operacje manipulacji pojedynczymi bitami (RMB, SMB, BBR i BBS), 192 bajty pamięci RAM o zerowej stronie, UART itp. |

| Rockwella | R65F11 R65F12 |

Rockwell R65F11 (wprowadzony w 1983 r.) i późniejszy R65F12 to ulepszone wersje procesora opartego na 6502, obejmujące również operacje manipulacji pojedynczymi bitami (RMB, SMB, BBR i BBS), pamięć RAM na chipie z zerową stroną, Forth na chipie ROM jądra, UART itp. |

| GTE | G65SC102 | Oprogramowanie kompatybilne z 65C02, ale ma nieco inny układ pinout i oscylatora. BBC Mistrz Turbo zawarte w wersji 4 MHz tego procesora na karcie koprocesora, które mogłyby również być zakupiony oddzielnie i dodawane do Master 128. |

| Rockwella | R65C00 R65C21 R65C29 |

R65C00, R65C21 i R65C29 zawierały dwa ulepszone CMOS 6502 w jednym układzie, a R65C00 i R65C21 dodatkowo zawierały 2 kB programowalnej pamięci ROM. |

| CM630 | Klon modelu 6502 z bloku wschodniego o częstotliwości 1 MHz i był używany w bułgarskich klonach serii Apple // Pravetz 8A i 8C . | |

| Technologia MOS |

7501 8501 |

Warianty 6510 (samego ulepszonego 6502), wprowadzonego w 1984 roku. Rozszerzyły liczbę pinów portu I/O z 6 do 7, ale pominęły piny dla przerwań niemaskowanych i wyjścia zegara. Używany w komputerach Commodore C-16 , C-116 i Plus/4 . Główna różnica między procesorami 7501 i 8501 polega na tym, że 7501 został wyprodukowany w procesie HMOS-1 , a 8501 w HMOS-2. |

| Technologia MOS | 8500 | Wprowadzony w 1985 roku jako wersja HMOS modelu 6510 (który z kolei bazuje na modelu 6502). Poza modyfikacją procesu, 8500 jest praktycznie identyczny z wersją 6510 NMOS. Zastąpił 6510 w późniejszych wersjach Commodore 64 . |

| Technologia MOS | 8502 | Zaprojektowany przez MOS Technology i używany w Commodore 128 . Oparty na MOS 6510 używanym w Commodore 64, 8502 był w stanie działać z podwójną częstotliwością zegara 6510. Rodzina 8502 obejmuje również MOS 7501, 8500 i 8501. |

| Hudson miękki | HuC6280 | Ulepszona wersja WDC 65C02 japońskiej firmy produkującej gry wideo Hudson Soft . Wyprodukowane dla nich przez Seiko Epson i NEC dla SuperGrafx . Najbardziej godnym uwagi produktem wykorzystującym HuC6280 jest konsola do gier wideo TurboGrafx-16 firmy NEC. |

16-bitowe pochodne

Western Design Center zaprojektowało i obecnie produkuje procesor W65C816S , 16-bitowy następca 65C02 z rdzeniem statycznym , ze znacznie ulepszonymi funkcjami. W65C816S to nowszy wariant 65C816, który stanowi rdzeń komputera Apple II GS i jest podstawą procesora Ricoh 5A22 , który zasila system Super Nintendo Entertainment System . W65C816S zawiera drobne ulepszenia w stosunku do 65C816, które sprawiają, że nowszy układ nie jest dokładnie kompatybilnym sprzętowo zamiennikiem wcześniejszego. Wśród tych ulepszeń była konwersja na rdzeń statyczny, który umożliwia zatrzymanie zegara w dowolnej fazie bez utraty danych w rejestrach. Dostępny za pośrednictwem dystrybutorów elektroniki, od marca 2020 r. W65C816S jest oficjalnie przystosowany do pracy z częstotliwością 14 MHz.

Western Design Center zaprojektowało i wyprodukowało również 65C802 , który był rdzeniem 65C816 z 64-kilobajtową przestrzenią adresową w pakiecie kompatybilnym z 65(C)02 pinami. 65C802 można zmodernizować do płyty 6502 i będzie działać jako 65C02 po włączeniu, działając w „trybie emulacji”. Podobnie jak w przypadku 65C816, sekwencja dwóch instrukcji przełączy 65C802 w tryb „natywny”, odsłaniając 16-bitowy akumulator i rejestry indeksowe , a także inne ulepszone funkcje 65C816. 65C802 nie był powszechnie używany; nowe projekty prawie zawsze były budowane wokół 65C816, w wyniku czego produkcja 65C802 została przerwana.

Przykładowy kod

Poniższy kod źródłowy języka asembler 6502 jest dla podprogramu o nazwie , który kopiuje łańcuch znaków zakończony znakiem null z jednej lokalizacji do drugiej, konwertując wielkie litery na małe litery. Kopiowany ciąg to „źródło”, a ciąg, w którym przechowywane jest przekonwertowane źródło, to „miejsce docelowe”.

TOLOWER

0080

0080 00 04

0082 00 05

0600

0600 A0 00

0602 B1 80

0604 F0 11

0606 C9 41

0608 90 06

060A C9 5B

060C B0 02

060E 09 20

0610 91 82

0612 C8

0613 D0 ED

0615 38

0616 60

0617 91 82

0619 18

061A 60

061B

|

; TOLOWER:

;

; Convert a null-terminated character string to all lower case.

; Maximum string length is 255 characters, plus the null term-

; inator.

;

; Parameters:

;

; SRC - Source string address

; DST - Destination string address

;

ORG $0080

;

SRC .WORD $0400 ;source string pointer

DST .WORD $0500 ;destination string pointer

;

ORG $0600 ;execution start address

;

TOLOWER LDY #$00 ;starting index

;

LOOP LDA (SRC),Y ;get from source string

BEQ DONE ;end of string

;

CMP #'A' ;if lower than UC alphabet...

BCC SKIP ;copy unchanged

;

CMP #'Z'+1 ;if greater than UC alphabet...

BCS SKIP ;copy unchanged

;

ORA #%00100000 ;convert to lower case

;

SKIP STA (DST),Y ;store to destination string

INY ;bump index

BNE LOOP ;next character

;

; NOTE: If Y wraps the destination string will be left in an undefined

; state. We set carry to indicate this to the calling function.

;

SEC ;report string too long error &...

RTS ;return to caller

;

DONE STA (DST),Y ;terminate destination string

CLC ;report conversion completed &...

RTS ;return to caller

;

.END

|

Błędy i dziwactwa

6502 miał kilka błędów i dziwactw, które trzeba było uwzględnić podczas programowania:

- Najwcześniejsze wersje 6502, takie jak te dostarczane z niektórymi komputerami KIM-1 , miały poważny błąd w instrukcji ROR (obróć prawą pamięć lub akumulator). Działanie ROR w tych układach jest w rzeczywistości instrukcją ASL (arytmetyczne przesunięcie w lewo), która nie wpływa na bit przeniesienia w rejestrze stanu. MOS opuścił instrukcję z dokumentacji układu całkowicie z powodu defektu, obiecując, że ROR pojawi się na układach 6502 począwszy od 1976 roku. Ogromna większość istniejących obecnie układów 6502 nie wykazuje tego błędu.

- Rodzina NMOS 6502 ma wiele nieudokumentowanych instrukcji , które różnią się w zależności od producenta chipów. Dekodowanie instrukcji 6502 jest zaimplementowane w przewodowej tablicy logicznej (podobnej do programowalnej tablicy logicznej ), która jest zdefiniowana tylko dla 151 z 256 dostępnych opkodów . Pozostałe 105 wyzwala dziwne i czasami trudne do przewidzenia działania, takie jak awaria procesora, wykonywanie dwóch ważnych instrukcji kolejno, wykonywanie dziwnych mieszanek dwóch instrukcji lub po prostu nie robienie nic. Firma Eastern House Software opracowała „Trap65”, urządzenie, które podłącza się między procesorem a jego gniazdem w celu konwersji (pułapki) niezaimplementowanych opkodów na instrukcje BRK (przerwania programowego). Niektórzy programiści wykorzystywali tę cechę do rozszerzenia zestawu instrukcji 6502 poprzez zapewnienie funkcjonalności dla niezaimplementowanych opkodów za pomocą specjalnie napisanego oprogramowania przechwyconego w wektorze 0xFFFE instrukcji BRK. Wszystkie niezdefiniowane kody operacji zostały zastąpione instrukcjami NOP w 65C02 , ulepszonej wersji CMOS 6502, chociaż z różnymi rozmiarami bajtów i czasami wykonania. W 65C802/65C816 wszystkie 256 opkodów wykonują określone operacje.

- Instrukcja pośredniego skoku pamięci 6502 ,

JMP (<address>), jest częściowo zepsuta. Jeśli <adres> jest szesnastkowy xxFF (tj. dowolne słowo kończące się na FF ), procesor nie przeskoczy do adresu zapisanego w xxFF ixxFF+1zgodnie z oczekiwaniami, ale raczej do adresu zdefiniowanego przez xxFF i xx00 (na przykładJMP ($10FF)przeskoczy do adresu przechowywany w 10FF i 1000, zamiast w 10FF i 1100). Wada ta trwała przez całą linię NMOS, ale została skorygowana w pochodnych CMOS. - Zindeksowane adresowanie NMOS 6502 ponad granicami strony wykona dodatkowy odczyt nieprawidłowego adresu. Ta cecha może powodować losowe problemy podczas uzyskiwania dostępu do sprzętu działającego na odczycie, takiego jak licznik czasu zerowania lub flagi IRQ, wysyłanie uzgadniania we/wy itp. Ta usterka trwała przez całą linię NMOS, ale została naprawiona w pochodnych CMOS, w który procesor wykonuje dodatkowy odczyt ostatniego bajtu instrukcji.

- Instrukcje odczytu-modyfikacji-zapisu 6502 wykonują jeden cykl odczytu i dwa cykle zapisu. Najpierw odczytane niezmodyfikowane dane są zapisywane z powrotem, a następnie zapisywane są dane zmodyfikowane. Ta cecha może powodować problemy przez dwukrotny dostęp do sprzętu działającego podczas zapisu. Ta anomalia trwała przez całą linię NMOS, ale została naprawiona w pochodnych CMOS, w których procesor wykona dwa odczyty i jeden cykl zapisu. Defensywna praktyka programowania generalnie pozwoli uniknąć tego problemu, nie wykonując instrukcji odczytu/modyfikacji/zapisu na rejestrach sprzętowych.

- Flagi stanu N (wynik ujemny), V (przepełnienie bitu znaku) i Z (wynik zero) są generalnie bez znaczenia podczas wykonywania operacji arytmetycznych, gdy procesor jest w trybie BCD , ponieważ te flagi odzwierciedlają wynik binarny, a nie BCD. To ograniczenie zostało usunięte w pochodnych CMOS. Dlatego ta funkcja może być wykorzystana do odróżnienia procesora CMOS od wersji NMOS.

- Jeśli 6502 znajdzie się w trybie BCD, gdy wystąpi przerwanie sprzętowe, nie powróci do trybu binarnego. Ta cecha może skutkować niejasnymi błędami w procedurze obsługi przerwań, jeśli nie wyczyści trybu BCD przed wykonaniem jakichkolwiek operacji arytmetycznych. Na przykład, C64 „s Kernal nieprawidłowo obsługiwać tę cechę procesora, wymagając Przerwania są wyłączone lub ponownego wektorowego BCD podczas operacji matematycznych. Ten problem rozwiązano również w pochodnych CMOS.

- Zestaw instrukcji 6502 zawiera BRK (kod operacyjny 00 $), który jest technicznie przerwaniem programowym (podobnym duchem do mnemonika SWI procesorów Motorola 6800 i ARM ). BRK jest najczęściej używany do przerwania wykonywania programu i uruchomienia monitora języka maszynowego do testowania i debugowania podczas tworzenia oprogramowania. BRK może być również używany do kierowania wykonania programu przy użyciu prostej tablicy skoków (analogicznie do sposobu, w jaki Intel 8086 i pochodne obsługują przerwania programowe według liczby). Jednakże, jeśli przerwanie sprzętowe wystąpi, gdy procesor pobiera instrukcję BRK, wersja NMOS procesora nie wykona BRK i zamiast tego będzie postępować tak, jakby wystąpiło tylko przerwanie sprzętowe. Ta usterka została naprawiona w implementacji CMOS procesora.

- Podczas wykonywania instrukcji JSR (skok do podprogramu) i RTS (powrót z podprogramu), adres powrotu wepchnięty na stos przez JSR jest adresem ostatniego bajtu operandu JSR (czyli najbardziej znaczącego bajtu adresu podprogramu), zamiast adresu poniższej instrukcji. Dzieje się tak, ponieważ właściwa kopia (od licznika programu do stosu i odwrotnie) ma miejsce przed automatycznym przyrostem licznika programu, który występuje na końcu każdej instrukcji. Ta cecha pozostanie niezauważona, chyba że kod zbada adres zwrotny w celu pobrania parametrów w strumieniu kodu (idiom programowania 6502 udokumentowany w Podręczniku technicznym ProDOS 8 ). Do dziś pozostaje charakterystyczną cechą 6502 pochodnych.

Zobacz też

- Lista 6502 monterów

- Komputery domowe oparte na technologii MOS 6502

- Przerwy w procesorach 65xx

- Liczba tranzystorów

- Akceleratory Apple II

- cc65 - 6502 asembler makr i kompilator C

Uwagi

Bibliografia

Cytaty

Bibliografia

- Peddle, Chuck (12 czerwca 2014). „Historia ustna Chuck Peddle” (wywiad). Wywiad przeprowadził Doug Fairbairn i Stephen Diamond.

- Bagnall, Brian (2010). Commodore, firma na krawędzi (wyd. 2). Winnipeg, Manitoba: Wariant Press. Numer ISBN 978-0-9738649-6-0.

- Bennetta, Thomasa; Ekiss, John; Lattin, William (Bill); Lavell, Jeff (28 marca 2008). „Panel historii mówionej Motorola 6800” (PDF) (wywiad). Wywiad przeprowadził David Laws.

- Cushman, Robert H. (20 września 1975). „Części 2-1/2 generacji μP za 10 USD, które działają jak low-endowe mini” (PDF) . EDN . Boston: Cahners Publishing. 20 (17): 36-42. Zarchiwizowane z oryginału (PDF) w dniu 24 kwietnia 2016 r.

- Wywiad z Williamem Menschem Stanfordem i Projektem Doliny Krzemowej, 9 października 1995. Transkrypcja

Dalsza lektura

- Arkusze danych i instrukcje

- Karta katalogowa serii 6500 ; Technologia MOS; 12 stron; 1976.

- Podręcznik sprzętu serii 6500 ; drugie wydanie; Technologia MOS; 182 strony; 1976.

- Podręcznik programowania serii 6500 ; drugie wydanie; Technologia MOS; 262 strony; 1976.

- Książki

- 6502 Księga wniosków ; 1-sze wydanie; Rodnay Zaks ; Sybex; 281 stron; 1979; ISBN 978-0895880154 . (archiwum)

- 6502 Programowanie w asemblerze ; drugie wydanie; Lance Leventhal; Osborne/McGraw-Hill; 650 stron; 1986; ISBN 978-0078812163 . (archiwum)

- 6502 Podprogramy języka asemblera ; 1-sze wydanie; Lance Leventhal i Winthrop Saville; Osborne/McGraw-Hill; 550 stron; 1982; ISBN 978-0931988592 . (archiwum)

- 6502 Gry ; 1-sze wydanie; Rodnay Zaksa; Sybex; 292 strony; 1980; ISBN 978-0895880222 . (archiwum)

- 6502 Instrukcja obsługi ; 1-sze wydanie; Józefa Carra; Reston; 288 stron; 1984; ISBN 978-0835970020 . (archiwum)

- Zaawansowane programowanie 6502 ; 1-sze wydanie; Rodnay Zaksa; John Wiley & Synowie; 292 strony; 1982; ISBN 978-0895880895 . (archiwum)

- Język maszynowy dla początkujących - komputer osobisty Programowanie języka maszynowego dla komputerów Atari, VIC, Apple, C64 i PET ; 1-sze wydanie; Richarda Mansfielda; Obliczać! Publikacje; 350 stron; 1983; ISBN 978-0942386110 . (archiwum)

- Programowanie 6502 ; 4 wydanie; Rodnay Zaksa; Sybex; 408 stron; 1983; ISBN 978-0895881359 . (archiwum)

- Programowanie 65816 - w tym 6502, 65C02 , 65802 ; 1-sze wydanie; David Eyes i Ron Lichty; Sala urzędnicza; 636 stron; 1986; ISBN 978-0893037895 . (archiwum)

- Karty referencyjne

- 6502 Mikroprocesorowa karta natychmiastowego odniesienia ; Jamesa Lewisa; mikrologika; 2 strony; 1980. (archiwum)

Zewnętrzne linki

- 6502.org - zasób mikroprocesora 6502 – repozytorium

- Rozwój technologii MOS i 6502 — archiwum Commodore

- Informacje 650x – Zwięzły opis, zdjęcia układów MOS i drugiego źródła; w cpu-collection.de

- mdfs.net – zestaw instrukcji 6502

- Sprytny Eric. "6502 - pierwszy RISC µP" . Zarchiwizowane od oryginału w dniu 24 maja 2012 r.

- Harrod, Dennette A. (październik 1980). "6502 Pobiera instrukcje mikroprogramowalne" . bajt . Tom. 5 nie. 10. Wzgórze McGrawa . s. 282-285. ISSN 0360-5280 . Zarchiwizowane od oryginału w dniu 2006-05-25 . Źródło 2006-05-14 .

- Symulatory / Emulatory

- Assembler i emulator online zgodny z 6502, napisany w JavaScript Zarchiwizowane 2011-02-08 w Wayback Machine

- Lista emulatorów oprogramowania 6502 – Domena Zophara

- Symulator 6502 dla Windows – Atari Gaming Headquarters

- Wizualna symulacja na poziomie tranzystora procesora 6502

- Rdzeń procesora MCL65 6502 - kod C - MicroCore Labs GitHub

- Tablice

- Płyta Grant's 7/8-chip 6502

- 6502 mikroprocesorowa płyta szkoleniowa

- Zbuduj własną tablicę treningową KIM-1 - zobacz KIM-1

- 6502 komputer domowy

- Komputer jednopłytkowy PE6502

- Komputer jednopłytkowy BE6502 — na podstawie filmów Ben Eater

- FPGA

- cpu6502_tc 6502 rdzeń procesora - kod źródłowy VHDL - OpenCores

- ag_6502 6502 rdzeń procesora - kod źródłowy Verilog - OpenCores

- Rdzeń procesora M65C02 65C02 — kod źródłowy Verilog — OpenCores

- Rdzeń procesora MCL65 6502 — Verilog — MicroCore Labs GitHub